US007638379B2

# (12) United States Patent Cheng et al.

# (10) Patent No.:

US 7,638,379 B2

(45) Date of Patent:

Dec. 29, 2009

# (54) VERTICAL-CHANNEL JUNCTION FIELD-EFFECT TRANSISTORS HAVING BURIED GATES AND METHODS OF MAKING

MAKING

(75) Inventors: Lin Cheng, Starkville, MS (US);

Michael S. Mazzola, Starkville, MS

(US)

(73) Assignees: SemiSouth Laboratories, Inc.,

(73) Assignees: SemiSouth Laboratories, Inc., Starkville, MI (US); Mississippi State University, Mississippi State, MI (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/935,442

(22) Filed: Nov. 6, 2007

(65) Prior Publication Data

US 2008/0124853 A1 May 29, 2008

# Related U.S. Application Data

- (62) Division of application No. 11/198,298, filed on Aug. 8, 2005.

- (51) Int. Cl. *H01L 21/337* (2006.01)

- (52) U.S. Cl. ...... 438/193; 438/195; 257/E21.421

(56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,587,712 | A |   | 5/1986  | Baliga     |         |

|-----------|---|---|---------|------------|---------|

| 5,264,713 | A |   | 11/1993 | Palmour    |         |

| 5,391,895 | A |   | 2/1995  | Dreifus    |         |

| 5,468,661 | Α | * | 11/1995 | Yuan et al | 438/193 |

| 5,747,842 | Α |   | 5/1998  | Plumton    |         |

2)

#### (Continued)

5,909,110 A \* 6/1999 Yuan et al. ...... 323/282

## FOREIGN PATENT DOCUMENTS

WO

00/38246 A1 6/2000

#### OTHER PUBLICATIONS

"Top Performance of SiC Power Transistor Designed for Inverters," Translation of AIST press released on Mar. 28, 2005.

#### (Continued)

Primary Examiner—Savitri Mulpuri

Assistant Examiner—Calvin Choi

(74) Attorney, Agent, or Firm—Morris, Manning & Martin,

LLP; Christopher W. Raimund

# (57) ABSTRACT

Semiconductor devices and methods of making the devices are described. The devices can be implemented in SiC and can include epitaxially grown n-type drift and p-type trenched gate regions, and an n-type epitaxially regrown channel region on top of the trenched p-gate regions. A source region can be epitaxially regrown on top of the channel region or selectively implanted into the channel region. Ohmic contacts to the source, gate and drain regions can then be formed. The devices can include edge termination structures such as guard rings, junction termination extensions (JTE), or other suitable p-n blocking structures. The devices can be fabricated with different threshold voltages, and can be implemented for both depletion and enhanced modes of operation for the same channel doping. The devices can be used as discrete power transistors and in digital, analog, and monolithic microwave integrated circuits.

#### 14 Claims, 12 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,910,665    | A   | 6/1999  | Plumton et al.      |

|--------------|-----|---------|---------------------|

| 6,097,046    | A * | 8/2000  | Plumton 257/266     |

| 6,344,663    | B1  | 2/2002  | Slater, Jr. et al.  |

| 6,503,782    | B2  | 1/2003  | Casady et al.       |

| 6,767,783    | B2  | 7/2004  | Casady et al.       |

| 7,105,875    | B2  | 9/2006  | Singh               |

| 7,119,380    | B2  | 10/2006 | Sankin et al.       |

| 2003/0042538 | A1* | 3/2003  | Kumar et al 257/328 |

| 2005/0067630 | AI  | 3/2005  | Zhao                |

#### OTHER PUBLICATIONS

J. W. Palmour, et al., "Low-frequency noise in 4H—silicon carbide junction field effect transistors," Appl. Phys. Lett. vol. 68, No. 19, May 6, 1996.

P.G. Neudeck, et al., "600° C. Logic Gates Using Silicon Carbide JFET's," NASA/TM-2000-209928, National Aeronautics and space Administration, Glenn Research Center, pp. 1-4.

J. N. Merrett, et al., "Gamma and Proton Irradiation Effects on 4H-SiC Depletion-Mode Trench JFETs," Materials Science Form, vols. 483-485, pp. 885-888, 2005.

L. Cheng, et al., "Cryogenic and High Temperature Performance of 4H-SiC Vertical Junction Field Effect Transistors (VJFETs) for Space Applications," Proceedings of The 17th International Symposium on Power Semiconductor Devices and ICs (ISPSD '05), May 22-26, 2005, Santa Barbara, CA.

J.N. Merrett, et al., "Silicon Carbide Vertical Junction Field Effect Transistors Operated at Junction Temperatures Exceeding 300° C.," Proceedings of IMAPS International Conference and Exhibition on High Temperature Electronics (HiTECH 2004), May 17-20, 2004, Santa Fe, NM.

S. Onda, et al., "SiC Integrated MOSFETs," Phys. Stat. Sol. (a), vol. 162, p. 369-388, 1997.

N. Nordell, et al., "Homoepitaxy of 6H and 4H SiC on nonplanar substrates," Appl. Phys. Lett., vol. 72, No. 2, pp. 197-199, Jan. 12, 1008

Y. Chen, et al., "Homoepitaxial Growth of 4H-SiC on Trenched Substrates by Chemical Vapor Deposition," Mater. Sci. Forum, vol. 457-460, pp. 189-192, 2004.

K. Shenai, et al., "Optimum Semiconductors for High Power Electronics", IEEE Transactions on Electron Devices, vol. 36, No. 9, pp. 1811-1823, 1989.

Chen, Yi, "Homoepitaxial Growth of 4H-SiC on Trenched Substrates by Chemical Vapor Deposition," Materials Science Forum, vols. 457-460 (2004), pp. 189-192.

Cheng, L., "Cryogenic and High Temperature Performance of 4H-SiC Vertical Junction Field Effect Transistors (VJFETs) for Space Applications," Proceedings of the 17<sup>th</sup> International Symposium on Power Semiconductor Devices & IC's, May 23-26, 2005. Merrett, J.N., "Silicon Carbide Vertical Junction Field Effect Transistors Operated at Junction Temperatures Exceeding 300° C.,"Dept. of Electrical and Computer Engineering, Mississippi State Univer-

Merrett, J.N., "Gamma and Proton Irradiation Effects on 4H-SIC Depletion-Mode Trench JFETs," Materials Science Form, vols. 483-485 (2005), pp. 885-888.

Neudeck, Philip G. et al., "600° C. Logic Gates Using Silicon Carbide JFET's," NASA/TM-2000-209928, National Aeronautics and Space Administration, Glenn Research Center., pp. 1-4.

Nordell, N. et al., "Homoepitaxy of 6H and 4H SiC on nonplanar substrates," Appl. Phys. Lett. 72 (2), Jan. 12, 1998.

Onda, S. et al., "SiC Integrated MOSFETs," Phys. Stat. Sol. (a), 162, (1997), pp. 369-388.

Palmour, J.W., "Low-frequency noise in 4H-silicon carbide junction field effect transistors," Appl. Phys. Lett. 68 (19), May 6, 1996.

"Top Performance of SiC Power Transistor Designed for Inverters," Translation of AIST press released on Mar. 28, 2005.

Mihalla, et al., "Buried field rings - a novel edge termination method for 4H-SiC high voltage devices," Semiconductor Conference, vol. 2, pp. 245-248 (2002).

<sup>\*</sup> cited by examiner

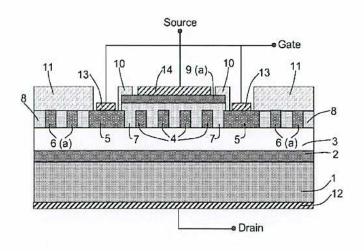

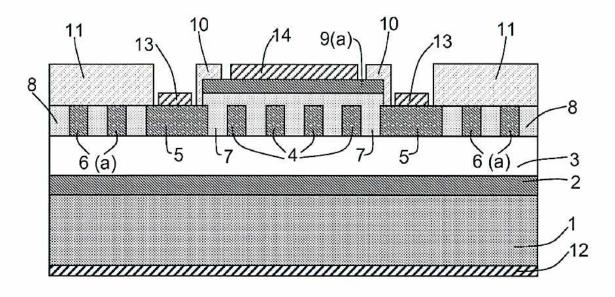

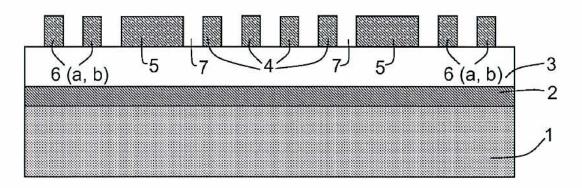

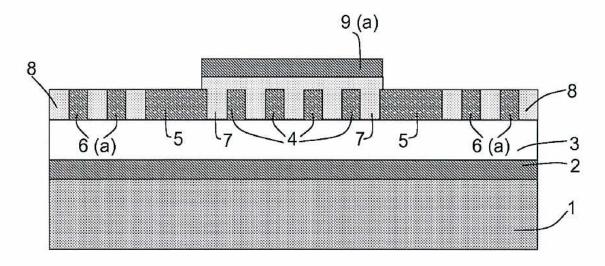

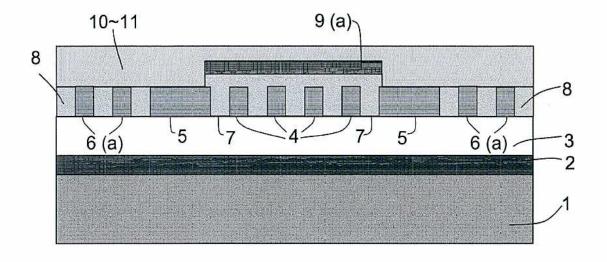

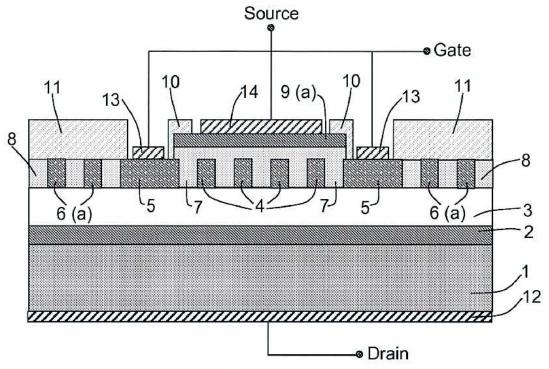

FIG. 1A

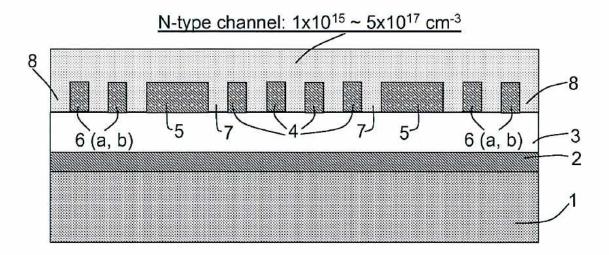

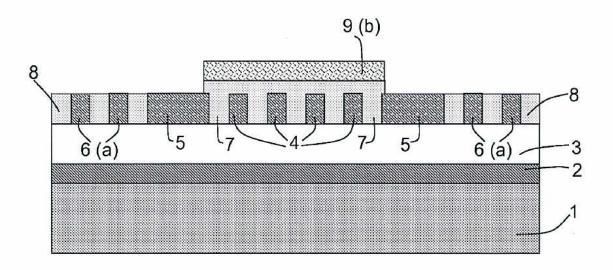

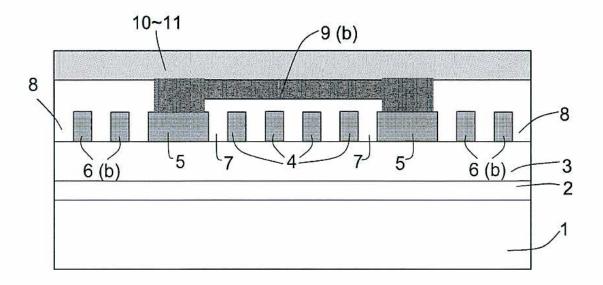

FIG. 1B

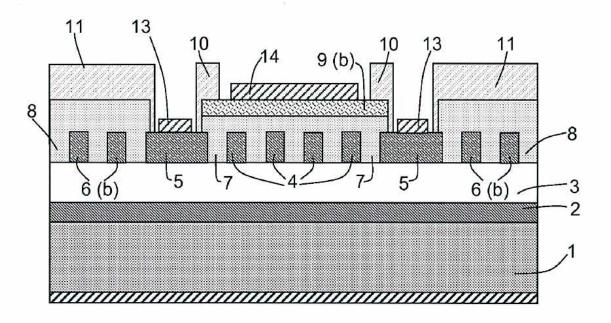

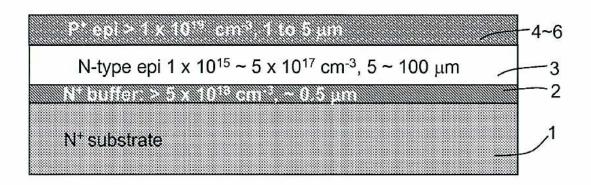

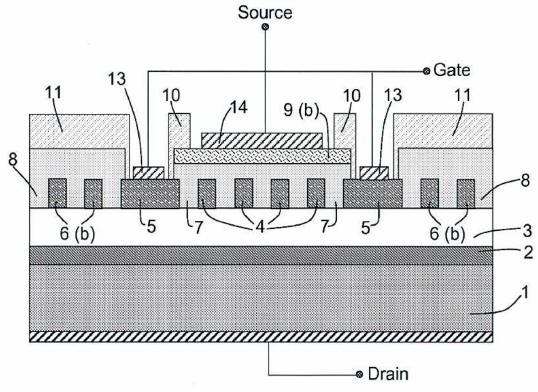

FIG. 2

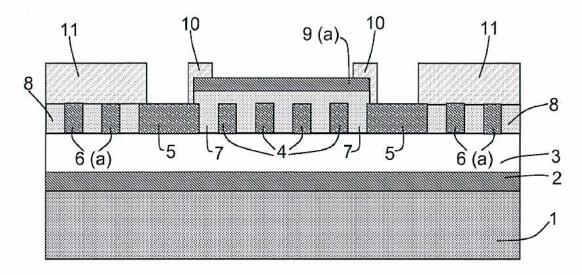

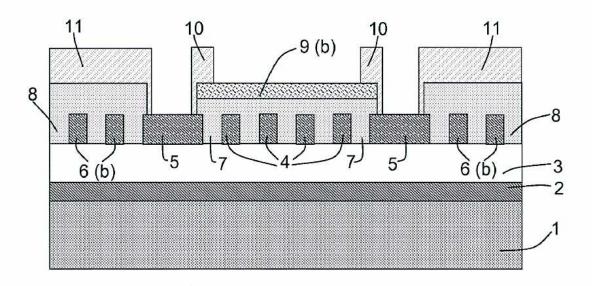

FIG. 3

FIG. 4

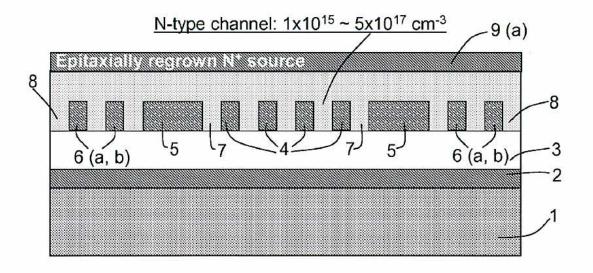

FIG. 5A

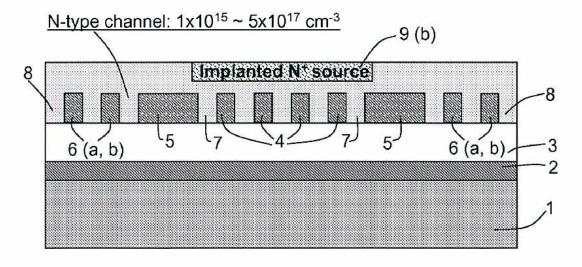

FIG. 5B

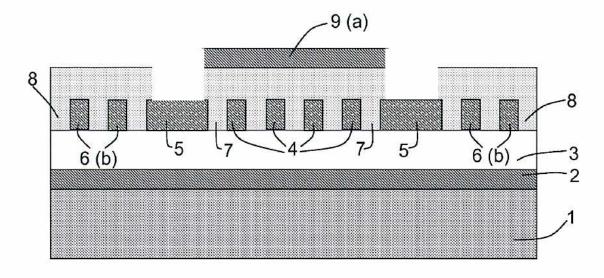

FIG. 6A

FIG. 6B

FIG. 6C

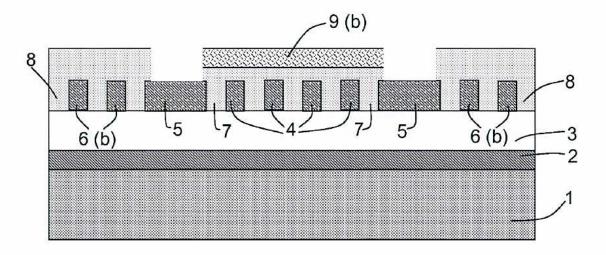

FIG. 6D

FIG. 7A

FIG. 7B

FIG. 8A

FIG. 8B

FIG. 9A

FIG. 9B

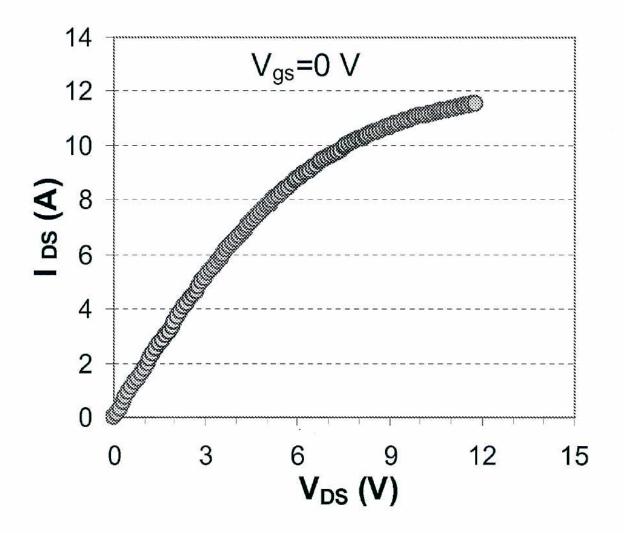

**FIG. 10A**

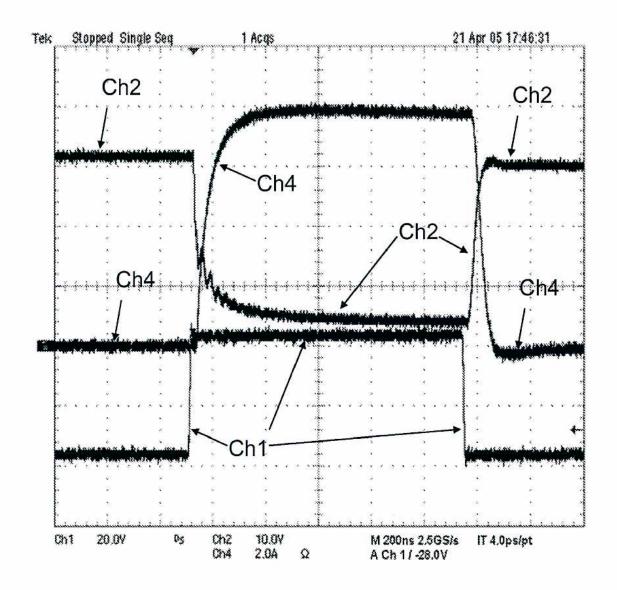

**FIG. 10B**

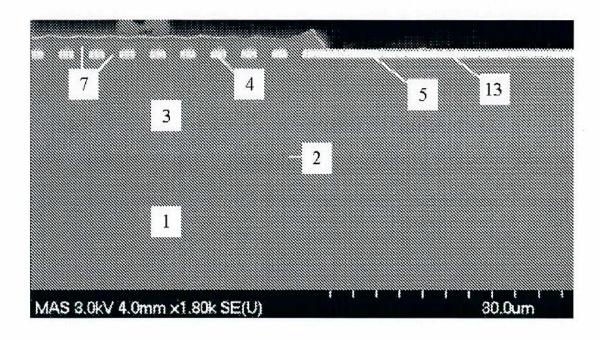

**FIG. 11A**

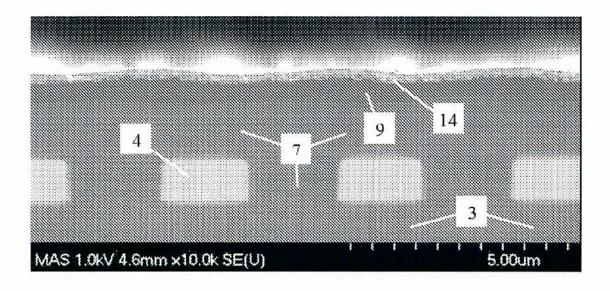

**FIG. 11B**

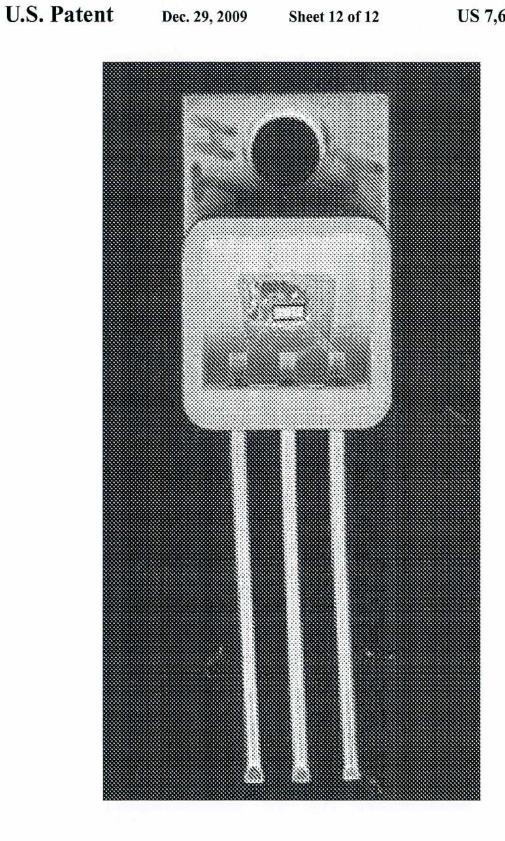

**FIG. 12**

20

1

# VERTICAL-CHANNEL JUNCTION FIELD-EFFECT TRANSISTORS HAVING BURIED GATES AND METHODS OF MAKING

#### CROSS REFERENCE TO RELATED CASES

This application is a divisional of U.S. patent application Ser. No. 11/198,298, filed on Aug. 8, 2005, which is incorporated by reference herein in its entirety.

# STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

This invention was made with U.S. Government support 15 under F33615-01-D-2103, awarded by the U.S. Air Force Research Laboratory. The U.S. Government may have certain rights in the invention.

#### BACKGROUND

1. Technical Field

The present application relates, in general, to semiconductor devices and, more particularly, to vertical-channel junction field effect transistors (VJFETs) having buried gates and to methods of making these devices.

2. Background of the Technology

Silicon Carbide (SiC), a wide band-gap semiconductor material, is very attractive for use in high-power, high-temperature, and/or radiation resistant electronics. SiC power switches are logical candidates for these applications due to their excellent material physical properties such as wide energy band-gap, high breakdown field strength, highly saturated electron drift velocity and high thermal conductivity compared to the conventional silicon counter part. In addition to the above advantages, SiC power devices can operate with lower specific on-resistance than conventional silicon power devices [1].

JFETs in SiC are especially attractive for high power applications thanks to the inherent stability of their p-n junction 40 gate, which is free from gate oxidation problems concerning channel mobility in MOS structure and high-temperature reliability issues in MESFETs having metal-semiconductor Schottky barrier.

Because of the fundamental differences in material properties and processing technologies, traditional Si or GaAs microelectronics technologies in JFETs can not be easily transferred to SiC. A number of reports of SiC JFETs have appeared in the last decade (e.g., [2-4]). An example of a vertical channel JFET employing a recessed gate structure 50 can be found in U.S. Pat. No. 4,587,712 [5]. An example of a lateral JFET formed in SiC can be found in U.S. Pat. No. 5,264,713 [2]. Enhanced-mode JFET for digital ICs with resistive load has been reported in 2000 [6]. JFET-based ICs can also be implemented in either complementary n-type and 55 p-type channels as disclosed in U.S. Pat. No. 6,503,782 [7] or enhanced-depletion (n-type channels) forms. SiC JFETs have proven to be radiation tolerant while demonstrating minimal threshold voltage shift over a wide temperature range [8, 9].

Most of the obstacles to low-cost volume manufacturing can be traced back to the gate-level process steps. In addition, the p-type gate contact can be difficult to fabricate in SiC because of the large band-gap of SiC. In fact, low resistivity contacts to p-type SiC have only been formed on heavily doped p-type SiC.

The VJFET (i.e., a JFET with a vertical channel structure) can be fabricated smaller than a JFET with a lateral channel 2

structure, which leads to lower cost in volume manufacturing of discrete transistors, and can also increase the packing density in large scale integrated circuits. To obtain a vertical channel in SiC VJFETs, ion implantation is often used to form the P+ gate region [8-10]. It can be difficult, however, to precisely control the channel length by ion implantation because of a combination of uncertainties on actual depth profile of implantation tail, defect density, redistribution of implanted ions after thermal annealing, and ionization percentage of dopant atoms and point defects under different bias and/or temperature stress.

Alternative methods to form a vertical channel have also been employed. One method is to selectively grow P<sup>+</sup> gate regions epitaxially as taught in U.S. Pat. No. 6,767,783 [11].

There still exists a need, however, for improved high volume, low cost manufacturing methods for VJFETs that allow for the precise control of channel length during manufacture.

#### SUMMARY

According to a first embodiment, a semiconductor device is provided which comprises:

a substrate layer comprising a semiconductor material of a first conductivity type;

a drift layer on the substrate layer, the drift layer comprising a semiconductor material of the first conductivity type:

a gate region on the drift layer, wherein the gate region comprises a semiconductor material of a second conductivity type different than the first conductivity type;

a channel layer of the first conductivity type on the drift layer and covering a first portion of the gate region; and

a source layer of the first conductivity type on the channel layer.

The drift layer of the device can be on a buffer layer comprising a semiconductor material of the first conductivity type wherein the buffer layer is on the semiconductor substrate. The semiconductor material of the substrate layer, the drift layer, the gate regions and the channel layer can be silicon carbide. The semiconductor material of the first conductivity type can be an n-type semiconductor material and the semiconductor material of the second conductivity type can be a p-type semiconductor material.

According to a second embodiment, a method of making a semiconductor device is provided which comprises:

selectively etching through a gate layer of semiconductor material of a second conductivity type on a drift layer of semiconductor material of a first conductivity type different than the second conductivity type to expose material of the drift layer, wherein the drift layer is on a semiconductor substrate:

depositing a channel layer of semiconductor material of the first conductivity type on exposed portions of the gate and drift layers to cover the gate layer;

depositing a source layer of semiconductor material of the first conductivity type on the channel layer or, alternatively, implanting a source layer of semiconductor material of the first conductivity type in the channel layer;

selectively etching through the channel layer in a peripheral region of the device to expose a portion of the underlying gate layer, wherein an unexposed portion of the gate layer of the device remains covered by the channel and source layers;

depositing a layer of a dielectric material on exposed surfaces of the source layer, the channel layer and the gate layer; selectively etching through the dielectric layer over the portion of the gate layer exposed during etching of the channel layer to expose underlying gate layer; and

selectively etching through the dielectric layer over the source layer on the unexposed portion of the gate layer to expose underlying source layer.

The channel layer can be deposited by epitaxial growth on exposed portions of the gate and drift layers. The source layer can be deposited by epitaxial growth on the channel layer or implanted in the channel layer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1A is a schematic 2-dimensional illustration of a multi-finger vertical trench JFET with an epitaxially regrown or selectively implanted source region and passivated guard

FIG. 1B is a schematic 2-dimensional illustration of a 15 multi-finger vertical trench JFET with epitaxially regrown or selectively implanted source region and buried guard rings.

FIG. 2 is a schematic diagram of a substrate with epitaxially grown N+ buffer, N-type drift, and P+ gate layers that can be used in the manufacture of a vertical trench JFET.

FIG. 3 is a schematic diagram of trenched P+ gate and guard ring regions formed on top of an N-type drift layer.

FIG. 4 is a schematic diagram of the P+ gate and guard ring regions of the structure shown in FIG. 3 trench-filled and 25 planarized with N-type channel layer.

FIG. 5A is a schematic diagram of the N+ source region homoepitaxially regrown on top of the N-type channel layer of the structure shown in FIG. 4.

FIG. 5B is a schematic diagram of the N<sup>+</sup> source region selectively implanted in the N-type channel layer of the structure shown in FIG. 4.

FIG. 6A is a schematic diagram of the N-type channel and source regions being patterned and etched back to expose the P+ gate pads and guard ring with epitaxially regrown N-type 35 source regions.

FIG. 6B a schematic diagram of the N-type channel and source regions being patterned and etched back to expose the P+ gate pads and guard ring with selectively implanted N-type

FIG. 6C is a schematic diagram of the N-type channel and source regions being patterned and etched back to expose P+ gate pads with buried guard ring and epitaxially regrown N-type source regions.

FIG. 6D is a schematic diagram of the N-type channel and 45 source regions being patterned and etched back to expose P+ gate pads with buried guard ring and selectively implanted N-type source regions.

FIG. 7A is a schematic diagram of the dielectric layer(s) being blanket deposited everywhere for both electrical isola-50 tion and passivation on top of the epitaxially regrown source and the exposed P+ gate pads and guard ring regions

FIG. 7B is a schematic diagram of the dielectric layer(s) being blanket deposited everywhere for both electrical isolaand the buried guard ring regions.

FIG. 8A is a schematic diagram of the dielectric layer(s) being patterned and etched back to open the metal contact windows on top of the gate and epitaxially regrown source regions.

FIG. 8B is a schematic diagram of the dielectric layer(s) being patterned and etched back to open the metal contact windows on top of the gate and selectively implanted source regions.

FIG. 9A is a schematic diagram of the metals being depos- 65 ited to form electrically conducting contacts to gate, drain, and epitaxially regrown source regions.

FIG. 9B is a schematic diagram of the metals being deposited to form electrically conducting contacts to gate, drain, and selectively implanted source regions.

FIG. 10A is a Scanning Electron Micrograph (SEM) of a buried-gate VJFET with self-planarizing epitaxially regrown channel and source regions.

FIG. 10B is a magnified SEM image of a buried-gate VJFET with epitaxially regrown self-planarizing channel and source.

FIG. 11A is a graph showing drain I-V characteristics at zero gate bias for an in-house fabricated VJFET in SiC having homoepitaxially grown drift, buried gate, planarized channel and source regions with 0.5 mm<sup>2</sup> active area.

FIG. 11B is a switching waveform measured at room temperature for an in-house fabricated VJFET in SiC having homoepitaxially grown drift, buried gate, planarized channel and source regions with 0.5 mm<sup>2</sup> active area.

FIG. 12 a photograph of a packaged VJFET in SiC according to one embodiment.

# REFERENCE NUMERALS

1. Substrate

N<sup>+</sup> buffer layer

3. N-type drift region

4. P-type buried gate fingers

5. P-type gate pads for metal contacts

6(a). P-type passivated guard rings

6(b). P-type buried guard rings

7. N-type planarized channel region

8. N-type trench-fill in guard ring regions

9(a). Homoepitaxially regrown N-type source region

9(b). Selectively implanted N-type source region

10. Isolation dielectric

11. Passivation dielectric

12. Drain metal contact

13. Gate metal contacts

14. Source metal contact

# DETAILED DESCRIPTION

An object of the present invention is to provide a verticalchannel Junction Field-Effect Transistor (JFET) with all epitaxially grown drift, buried gate, passivated or buried guard rings, planarized channel with either epitaxially grown or implanted source regions in SiC, that can be made electrically isolated from the other devices fabricated on the same die, and that can be implemented in such a way that the devices fabricated on the same die may have different threshold voltages.

A further object of the invention is to provide the concept and an example of planarization of trenched p-gate by homoepitaxial over-growth of channel and source regions on a silicon carbide patterned substrate.

A further object of the invention is to provide the concept tion and passivation on top of the selectively implanted source 55 and an example of planarization of trenched p-gate by homoepitaxial over-growth of only the channel region with the source region formed by implantation on a silicon carbide patterned substrate.

A further object of the invention is to provide a method of 60 the fabrication of the above devices.

The present application relates generally to a Junction Field-Effect Transistor (JFET) with vertical channel. In particular, the present application relates to such transistors formed in silicon carbide (SiC).

The present device is built on a silicon carbide substrate, which can be electrically either p-type or n-type with same type buffer layer. For using the n-type substrate, the device